# MIPI Alliance Standard for Display Serial Interface V1.0

MIPI Board approved 5 April 2006

## \* Caution to Implementers \*

This document is a MIPI Specification formally approved by the MIPI Alliance Board of Directors per the process defined in the MIPI Alliance Bylaws. However, the Display Working Group has identified certain technical issues in this approved version of the specification that are pending further review and which may require revisions of or corrections to this document in the near future. Such revisions, if any, will be handled via the formal specification revision process as defined in the Bylaws.

A Release Notes document has been prepared by the Display Working Group and is available to all members. The intent of the Release Notes is to provide a list of known technical issues under further discussion with the working group. This may not be an exhaustive list; its purpose is to simply catalog known issues as of this release date. Implementers of this specification should be aware of these facts, and take them into consideration as they work with the specification.

Release Notes for the Display Serial Interface Specification can be found at the following direct, permanent link:

https://www.mipi.org/members/file.asp?id=4844

# **MIPI Alliance Standard for Display Serial Interface**

Version 1.00a – 19 April 2006

MIPI Board Approved 5-Apr-2006

Further technical changes to DSI are expected as work continues in the Display Working Group

#### 1 NOTICE OF DISCLAIMER

2 The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI. The material contained herein is provided on 3 4 an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI hereby disclaim all 5 other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if 6 any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of 7 8 accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of 9 negligence.

ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET

POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD

TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY

AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR

MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE

MIPI BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE

GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL

GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL,

CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER

16 CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER

17 CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR

17 CONTRACT, TORT, WARRANTT, OR OTHERWISE, ARISING IN ANT WAT OUT OF THIS OR 18 ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL,

10 ANT OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL

19 WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH

20 DAMAGES.

21 Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is

22 further notified that MIPI: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the

23 contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document;

and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance

with the contents of this Document. The use or implementation of the contents of this Document may

involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents,

patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI. MIPI

does not make any search or investigation for IPR, nor does MIPI require or request the disclosure of any

28 does not make any search of investigation for IPK, nor does MIPI require of request the disclosu

29 IPR or claims of IPR as respects the contents of this Document or otherwise.

30 Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

31 MIPI Alliance, Inc.

- 32 c/o IEEE-ISTO

- 33 445 Hoes Lane

- 34 Piscataway, NJ 08854

- 35 Attn: Board Secretary

# 36 **Contents**

| 37 | Version | n 1.00 – 13 April 2006                                                   | i  |

|----|---------|--------------------------------------------------------------------------|----|

| 38 | 1 Ov    | /erview                                                                  | 8  |

| 39 | 1.1     | Scope                                                                    | 8  |

| 40 | 1.2     | Purpose                                                                  | 8  |

| 41 | 2 Te    | rminology (Informational)                                                | 9  |

| 42 | 2.1     | Definitions                                                              | 9  |

| 43 | 2.2     | Abbreviations                                                            | 10 |

| 44 | 2.3     | Acronyms                                                                 | 10 |

| 45 | 3 Re    | ferences (Informational)                                                 | 13 |

| 46 | 3.1     | DBI and DBI-2 (Display Bus Interface Standards for Parallel Signaling)   | 13 |

| 47 | 3.2     | DPI and DPI-2 (Display Pixel Interface Standards for Parallel Signaling) | 13 |

| 48 | 3.3     | DCS (Display Command Set)                                                | 14 |

| 49 | 3.4     | CSI-2 (Camera Serial Interface 2)                                        | 14 |

| 50 | 3.5     | D-PHY (MIPI Alliance Standard for Physical Layer)                        | 14 |

| 51 | 4 DS    | SI Introduction                                                          | 15 |

| 52 | 4.1     | DSI Layer Definitions                                                    | 16 |

| 53 | 4.2     | Command and Video Modes                                                  | 17 |

| 54 | 4.2     | 2.1 Command Mode                                                         | 17 |

| 55 | 4.2     | 2.2 Video Mode Operation                                                 | 17 |

| 56 | 4.2     | 2.3 Virtual Channel Capability                                           |    |

| 57 | 5 DS    | SI Physical Layer                                                        | 19 |

| 58 | 5.1     | Data Flow Control                                                        | 19 |

| 59 | 5.2     | Bidirectionality and Low Power Signaling Policy                          | 19 |

| 60 | 5.3     | Command Mode Interfaces                                                  | 20 |

| 61 | 5.4     | Video Mode Interfaces                                                    | 20 |

| 62 | 5.5     | Bidirectional Control Mechanism                                          | 20 |

| 63 | 5.6 Cl    | lock Management                                      | 21 |

|----|-----------|------------------------------------------------------|----|

| 64 | 5.6.1     | Clock Requirements                                   | 21 |

| 65 | 5.6.2     | Clock Power and Timing                               |    |

| 66 | 6 Multi-I | Lane Distribution and Merging                        | 23 |

| 67 | 6.1 M     | lulti-Lane Interoperability and Lane-number Mismatch |    |

| 68 | 6.1.1     | Clock Considerations with Multi-Lane                 | 25 |

| 69 | 6.1.2     | Bi-directionality and Multi-Lane Capability          | 25 |

| 70 | 6.1.3     | SoT and EoT in Multi-Lane Configurations             | 25 |

| 71 | 7 Low-L   | evel Protocol Errors and Contention                  |    |

| 72 | 7.1 Lo    | ow-Level Protocol Errors                             |    |

| 73 | 7.1.1     | SoT Error                                            |    |

| 74 | 7.1.2     | SoT Sync Error                                       |    |

| 75 | 7.1.3     | EoT Sync Error                                       |    |

| 76 | 7.1.4     | Escape Mode Entry Command Error                      |    |

| 77 | 7.1.5     | LP Transmission Sync Error                           |    |

| 78 | 7.1.6     | False Control Error                                  |    |

| 79 | 7.2 Co    | ontention Detection and Recovery                     |    |

| 80 | 7.2.1     | Contention Detection in LP Mode                      |    |

| 81 | 7.2.2     | Contention Recovery Using Timers                     |    |

| 82 | 7.3 A     | dditional Timers                                     |    |

| 83 | 7.3.1     | Turnaround Acknowledge Timeout (TA_TO)               |    |

| 84 | 7.3.2     | Peripheral Reset Timeout (PR_TO)                     |    |

| 85 | 7.4 A     | cknowledge and Error Reporting Mechanism             |    |

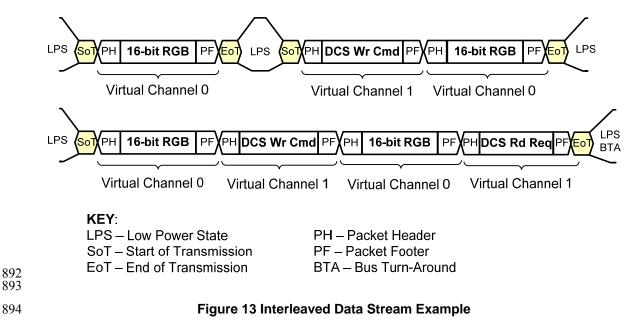

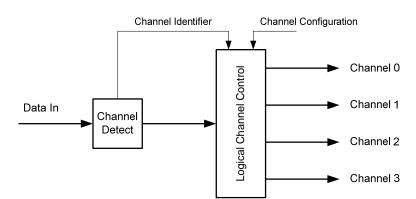

| 86 | 8 DSI Pr  | otocol                                               |    |

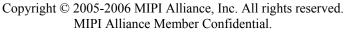

| 87 | 8.1 M     | Iultiple Packets per Transmission                    |    |

| 88 | 8.2 Pa    | acket Composition                                    |    |

| 89 | 8.3 Ei    | ndian Policy                                         |    |

| 90 | 8.4 G     | eneral Packet Structure                              |    |

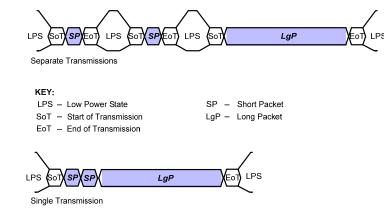

| 91  | 8.4.1    | Long Packet Format                                                                 | 38 |

|-----|----------|------------------------------------------------------------------------------------|----|

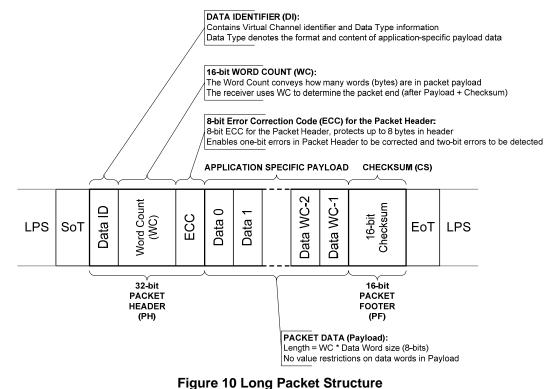

| 92  | 8.4.2    | Short Packet Format                                                                | 40 |

| 93  | 8.5 Coi  | mmon Packet Elements                                                               | 40 |

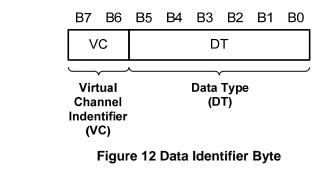

| 94  | 8.5.1    | Data Identifier Byte                                                               | 40 |

| 95  | 8.5.2    | Error Correction Code                                                              | 41 |

| 96  | 8.6 Inte | erleaved Data Streams                                                              | 41 |

| 97  | 8.6.1    | Interleaved Data Streams and Bi-directionality                                     | 42 |

| 98  | 8.7 Pro  | cessor to Peripheral Direction (Processor-Sourced) Packet Data Types               | 42 |

| 99  | 8.8 Pro  | cessor-to-Peripheral Transactions – Detailed Format Description                    | 43 |

| 100 | 8.8.1    | Sync Event (H Start, H End, V Start, V End), Data Type = xx 0001 (x1h)             | 43 |

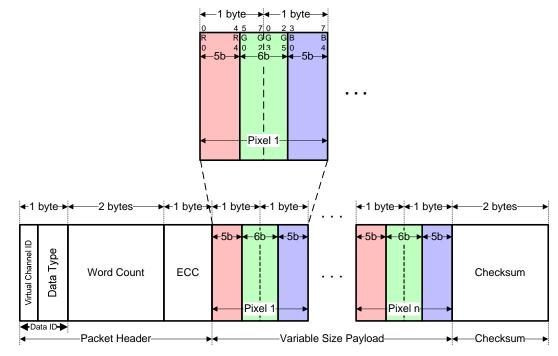

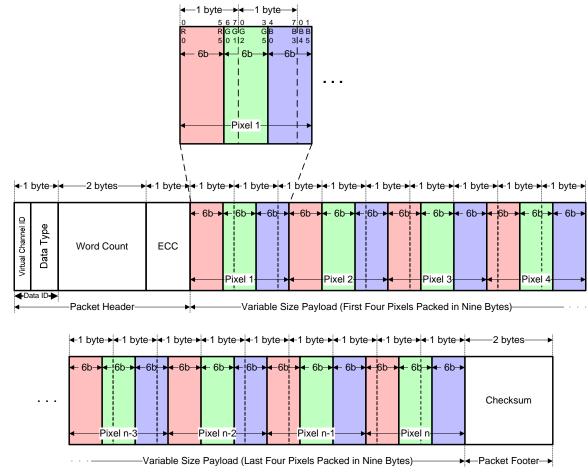

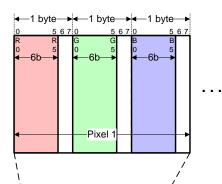

| 101 | 8.8.2    | Color Mode On Command, Data Type = 00 0010 (02h)                                   | 44 |

| 102 | 8.8.3    | Color Mode Off Command, Data Type = 01 0010 (12h)                                  | 44 |

| 103 | 8.8.4    | Shutdown Peripheral Command, Data Type = 10 0010 (22h)                             | 44 |

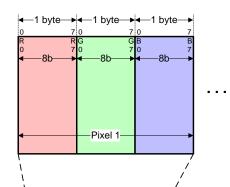

| 104 | 8.8.5    | Turn On Peripheral Command, Data Type = 11 0010 (32h)                              | 44 |

| 105 | 8.8.6    | Generic Short WRITE Packet, 0 to 7 Parameters, Data Type = xx x011 (x3h and xBh)   | 44 |

| 106 | 8.8.7    | Generic READ Request, 0 to 7 Parameters, Data Type = xx x100 (x4h and xCh)         | 44 |

| 107 | 8.8.8    | DCS Commands                                                                       | 45 |

| 108 | 8.8.9    | Set Maximum Return Packet Size, Data Type = 11 0111 (37h)                          | 46 |

| 109 | 8.8.10   | Null Packet (Long), Data Type = 00 1001 (09h)                                      | 46 |

| 110 | 8.8.11   | Blanking Packet (Long), Data Type = 01 1001 (19h)                                  | 46 |

| 111 | 8.8.12   | Generic Non-Image Data (Long), Data Type = 10 1001 (29h)                           | 47 |

| 112 | 8.8.13   | Packed Pixel Stream, 16-bit Format, Long packet, Data Type 00 1110 (0Eh)           | 47 |

| 113 | 8.8.14   | Packed Pixel Stream, 18-bit Format, Long packet, Data type = 01 1110 (1Eh)         | 48 |

| 114 | 8.8.15   | Pixel Stream, 18-bit Format in Three Bytes, Long packet, Data Type = 10 1110 (2Eh) | 49 |

| 115 | 8.8.16   | Packed Pixel Stream, 24-bit Format, Long packet, Data Type = 11 1110 (3Eh)         | 50 |

| 116 | 8.8.17   | DO NOT USE and Reserved Data Types                                                 | 50 |

| 117 | 8.9 Per  | ipheral-to-Processor (Reverse Direction) LP Transmissions                          | 51 |

| 118 | 8.9.1    | Packet Structure for Peripheral-to-Processor LP Transmissions                      | 51 |

|     |          |                                                                                    |    |

|            |                 | -                                                                             |        |

|------------|-----------------|-------------------------------------------------------------------------------|--------|

| 119        | 8.9.2           | System Requirements for ECC and Checksum and Packet Format                    | 51     |

| 120        | 8.9.3           | Appropriate Responses to Commands and ACK Requests                            | 52     |

| 121        | 8.9.4           | Format of Acknowledge with Error Report and Read Response Data Types          | 53     |

| 122        | 8.9.5           | Error-Reporting Format                                                        | 53     |

| 123        | 8.10 Per        | ipheral-to-Processor Transactions – Detailed Format Description               | 54     |

| 124        | 8.10.1          | Acknowledge with Error Report, Data Type 00 0010 (02h)                        | 55     |

| 125        | 8.10.2          | Generic Short Read Response with Optional ECC, Data Type 01 0xxx (10h - 17h)  | 55     |

| 126<br>127 | 8.10.3<br>(1Ah) | Generic Long Read Response with Optional ECC and Checksum, Data Type = $0$ 55 | 1 1010 |

| 128        | 8.10.4          | DCS Long Read Response with Optional ECC and Checksum, Data Type 01 1100 (10  | Ch)56  |

| 129        | 8.10.5          | DCS Short Read Response with Optional ECC, Data Type 10 0xxx (20h – 27h)      | 56     |

| 130        | 8.10.6          | Multiple-packet Transmission and Error Reporting                              | 56     |

| 131        | 8.10.7          | Clearing Error Bits                                                           | 56     |

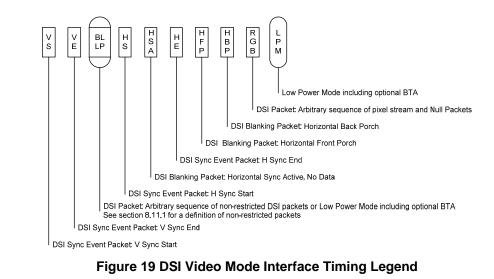

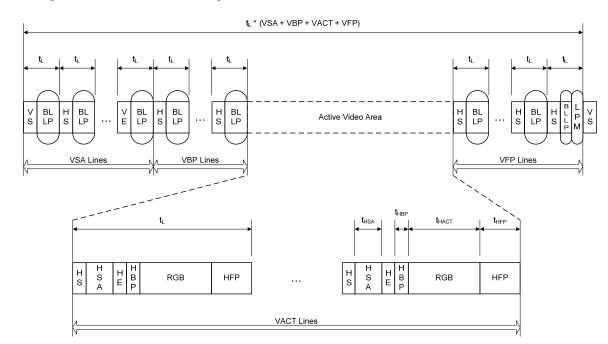

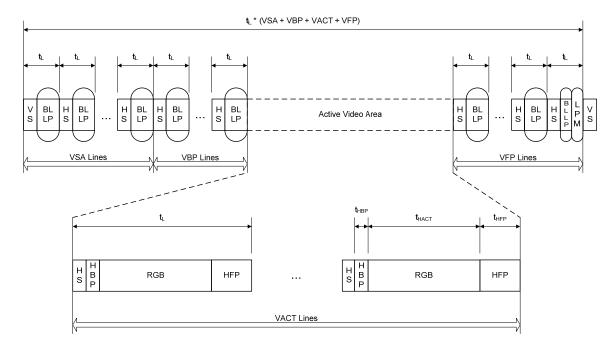

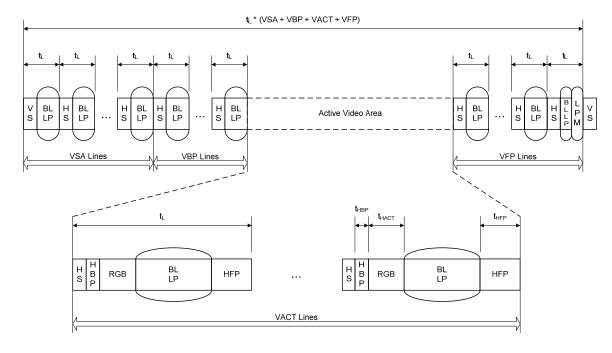

| 132        | 8.11 Vid        | eo Mode Interface Timing                                                      | 56     |

| 133        | 8.11.1          | Traffic Sequences                                                             | 57     |

| 134        | 8.11.2          | Non-Burst Mode with Sync Pulses                                               | 58     |

| 135        | 8.11.3          | Non-Burst Mode with Sync Events                                               | 58     |

| 136        | 8.11.4          | Burst Mode                                                                    | 59     |

| 137        | 8.11.5          | Parameters                                                                    | 60     |

| 138        | 8.12 TE         | Signaling in DSI                                                              | 61     |

| 139        | 9 Error-Co      | prrecting Code (ECC) and Checksum                                             | 63     |

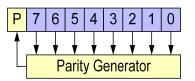

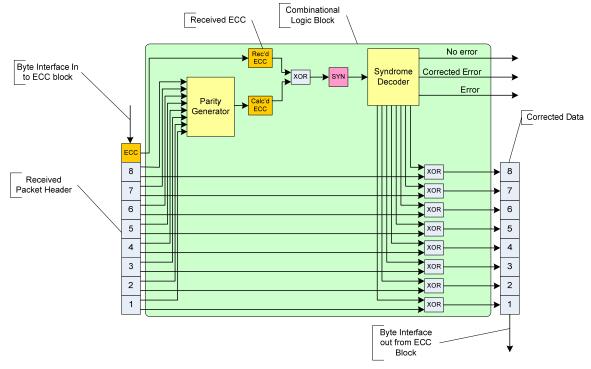

| 140        | 9.1 Har         | nming Code for Packet Header Error Detection/Correction                       | 63     |

| 141        | 9.2 Har         | nming-modified Code for DSI                                                   | 63     |

| 142        | 9.3 EC          | C Generation on the Transmitter and Byte-Padding                              | 67     |

| 143        | 9.4 App         | plying ECC and Byte-Padding on the Receiver                                   | 67     |

| 144        | 9.5 Che         | ecksum Generation for Long Packet Payloads                                    | 68     |

| 145        | 10 Comp         | liance, Interoperability, and Optional Capabilities                           | 70     |

| 146        | 10.1 Dis        | play Resolutions                                                              | 70     |

| 147 | 10.2    | Pixel Formats                                              | 71 |

|-----|---------|------------------------------------------------------------|----|

| 148 | 10.3    | Number of Lanes                                            | 71 |

| 149 | 10.4    | Maximum Lane Frequency                                     | 71 |

| 150 | 10.5    | Bidirectional Communication                                | 71 |

| 151 | 10.6    | ECC and Checksum Capabilities                              | 72 |

| 152 | 10.7    | Display Architecture                                       | 72 |

| 153 | 10.8    | Multiple Peripheral Support                                | 72 |

| 154 | Annex A | (Informative) Contention Detection and Recovery Mechanisms | 73 |

| 155 | A.1     | PHY Detected Contention                                    | 73 |

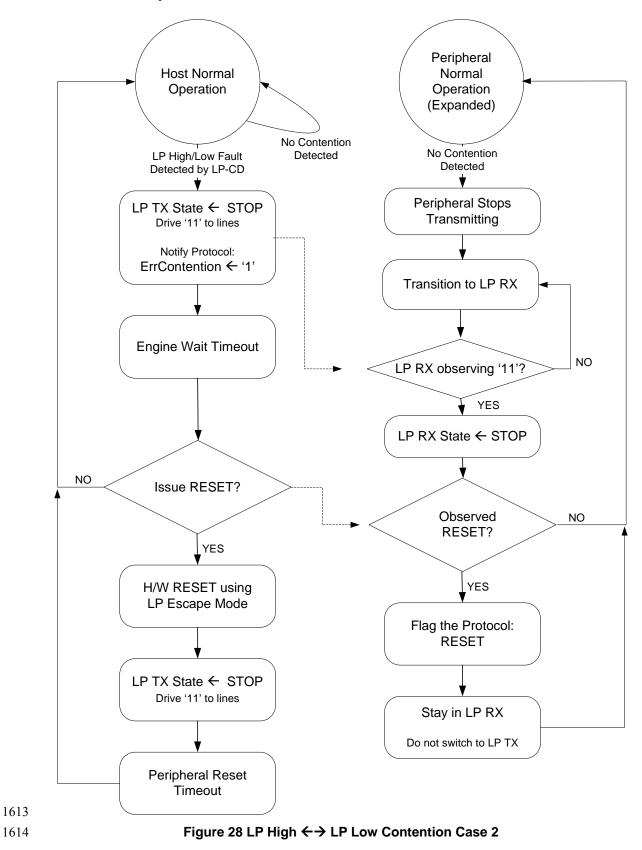

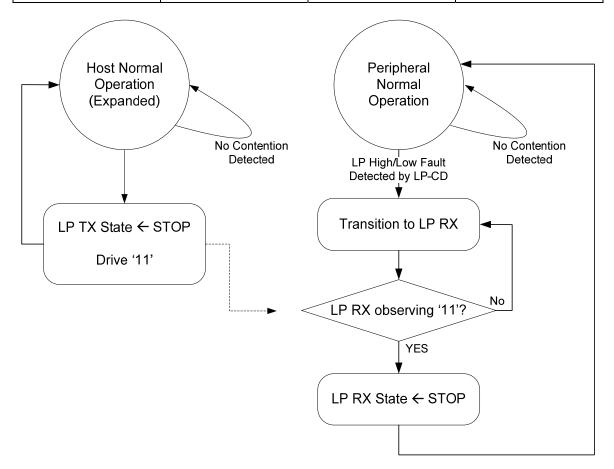

| 156 | A.1     | .1 Protocol Response to PHY Detected Faults                | 73 |

# 157 MIPI Alliance Standard for Display Serial Interface

### 158 **1 Overview**

The Display Serial Interface (DSI) specification defines protocols between a host processor and peripheral devices that adhere to MIPI Alliance specifications for mobile device interfaces. The DSI specification builds on existing standards by adopting pixel formats and command set defined in MIPI Alliance standards for DBI-2 [2], DPI-2 [3], and DCS [1].

### 163 **1.1 Scope**

164 Interface protocols as well as a description of signal timing relationships are within the scope of this 165 specification.

166 Electrical specifications and physical specifications are out of scope for this document. In addition, legacy

interfaces such as DPI-2 and DBI-2 are also out of scope for this specification. Furthermore, device usage of auxiliary buses such as  $I^2C$  or SPI, while not precluded by this specification, are also not within its scope.

# 170 **1.2 Purpose**

The Display Serial Interface specification defines a standard high-speed serial interface between a peripheral, such as an active-matrix display module, and a host processor in a mobile device. By standardizing this interface, components may be developed that provide higher performance, lower power, less EMI and fewer pins than current devices, while maintaining compatibility across products from multiple vendors.

### 176 **2** Terminology (Informational)

- The MIPI Alliance has adopted Section 13.1 of the IEEE Standards Style Manual, which dictates use of the words "shall", "should", "may", and "can" in the development of documentation, as follows:

- The word *shall* is used to indicate mandatory requirements strictly to be followed in order to conform to the standard and from which no deviation is permitted (*shall* equals *is required to*).

- 181 The use of the word *must* is deprecated and shall not be used when stating mandatory requirements; must is 182 used only to describe unavoidable situations.

- 183 The use of the word *will* is deprecated and shall not be used when stating mandatory requirements; *will* is 184 only used in statements of fact.

The word *should* is used to indicate that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required; or that (in the negative form) a certain course of action is deprecated but not prohibited (*should* equals *is recommended that*).

- 189 The word *may* is used to indicate a course of action permissible within the limits of the standard (*may* equals *is permitted*).

- 191 The word *can* is used for statements of possibility and capability, whether material, physical, or causal (*can* equals *is able to*).

- 193 All sections are normative, unless they are explicitly indicated to be informative.

#### 194 **2.1 Definitions**

- 195 Forward Direction: The signal direction is defined relative to the direction of the high-speed serial clock. 196 Transmission from the side sending the clock to the side receiving the clock is the forward direction.

- Half duplex: Bidirectional data transmission over a Lane allowing both transmission and reception butonly in one direction at a time.

- HS Transmission: Sending one or more packets in the forward direction in HS Mode. A HS Transmission

is delimited before and after packet transmission by LP-11 states.

- 201 Host Processor: Hardware and software that provides the core functionality of a mobile device.

- Lane: Consists of two complementary Lane Modules communicating via two-line, point-to-point Lane

Interconnects. A Lane is used for either Data or Clock signal transmission.

- Lane Interconnect: Two-line point-to-point interconnect used for both differential high-speed signaling and low-power single ended signaling.

- 206 Lane Module: Module at each side of the Lane for driving and/or receiving signals on the Lane.

- 207 Link: A complete connection between two devices containing one Clock Lane and at least one Data Lane.

- 208 LP Transmission: Sending one or more packets in either direction in LP Mode or Escape Mode. A LP 209 Transmission is delimited before and after packet transmission by LP-11 states.

- 210 Packet: A group of two or more bytes organized in a specified way to transfer data across the interface. All

- 211 packets have a minimum specified set of components. The byte is the fundamental unit of data from which 212 packets are made.

- Payload: Application data only with all Link synchronization, header, ECC and checksum and other

protocol-related information removed. This is the "core" of transmissions between host processor and

peripheral.

- 216 **PHY:** The set of Lane Modules on one side of a Link.

- PHY Configuration: A set of Lanes that represent a possible Link. A PHY configuration consists of a

minimum of two Lanes: one Clock Lane and one or more Data Lanes.

- 219 Reverse Direction: Reverse direction is the opposite of the forward direction. See the description for 220 Forward Direction.

- 221 Transmission: Refers to either HS or LP Transmission. See the HS Transmission and LP Transmission 222 definitions for descriptions of the different transmission modes.

- Virtual Channel: Multiple independent data streams for up to four peripherals are supported by this specification. The data stream for each peripheral is a *Virtual Channel*. These data streams may be interleaved and sent as sequential packets, with each packet dedicated to a particular peripheral or channel. Packet protocol includes information that directs each packet to its intended peripheral.

- 227 Word Count: Number of bytes.

- 228 2.2 Abbreviations

- 229 e.g. For example

#### 230 **2.3 Acronyms**

- 231 AM Active matrix (display technology)

- 232 AIP Application Independent Protocol

- 233 ASP Application Specific Protocol

- 234 BLLP Blanking or Low Power interval

- 235 BPP Bits per Pixel

- 236 BTA Bus Turn-Around

- 237 CSI Camera Serial Interface

- 238 DBI Display Bus Interface

- 239 DI Data Identifier

- 240 DMA Direct Memory Access

- 241 DPI Display Pixel Interface

- 242 DSI Display Serial Interface 243 DT Data Type 244 ECC Error-Correcting Code 245 EMI Electro Magnetic interference ЕоТ 246 End of Transmission 247 ESD Electrostatic Discharge 248 Fps Frames per second 249 HS High Speed 250 ISTO Industry Standards and Technology Organization 251 LLP Low-Level Protocol 252 LP Low Power 253 LPI Low Power Interval 254 LPS Low Power State (state of serial data line when not transferring high-speed serial data) LSB 255 Least Significant Bit 256 Mbps Megabits per second 257 MIPI Mobile Industry Processor Interface 258 MSB Most Significant Bit 259 PE Packet End 260 PF Packet Footer 261 PH Packet Header 262 PHY Physical Layer 263 ΡI Packet Identifier 264 PPI PHY-Protocol Interface 265 PS Packet Start

- 266 PT Packet Type

- 267 PWB Printed Wired Board

- 268 QCIF Quarter-size CIF (resolution 176x144 pixels or 144x176 pixels)

- 269 QVGA Quarter-size Video Graphics Array (resolution 320x240 pixels or 240x320 pixels)

- 270 RAM Random Access Memory

- 271 RGB Color presentation (Red, Green, Blue)

- 272 SLVS Scalable Low Voltage Signaling

- 273 SoT Start of Transmission

- 274 SVGA Super Video Graphics Array (resolution 800x600 pixels or 600x800 pixels)

- 275 VGA Video Graphics Array (resolution 640x480 pixels or 480x640 pixels)

- 276 VSA Vertical Sync Active

- 277 WVGA Wide VGA (resolution 800x480 pixels or 480x800 pixels)

- 278 WC Word Count

### 279 3 References (Informational)

- 280 [1] MIPI Alliance Standard for Display Command Set, version 1.00, April 2006

- 281 [2] MIPI Alliance Standard for Display Bus Interface, version 2.00, November 2005

- 282 [3] MIPI Alliance Standard for Display Parallel Interface, version 2.00, September 2005

- 283 [4] MIPI Alliance Standard for D-PHY, version 0.65, November 2005

- 284 Design and Analysis of Fault Tolerant Digital System by Barry W. Johnson

- 285 Error Correcting Codes: Hamming Distance by Don Johnson paper

- 286 Intel 8206 error detection and correction unit datasheet

- 287 National DP8400-2 Expandable Error Checker/Corrector datasheet

Much of DSI is based on existing MIPI Alliance standards as well as several MIPI Alliance standards in simultaneous development. In the Application Layer, DSI duplicates pixel formats used in *MIPI Alliance Standard for Display Parallel Interface* [3] when it is in *Video Mode* operation. For display modules with a display controller and frame buffer, DSI shares a common command set with *MIPI Alliance Standard for Display Bus Interface* [2]. The command set is documented in *MIPI Alliance Standard for Display Command Set* [1].

### 294 3.1 DBI and DBI-2 (Display Bus Interface Standards for Parallel Signaling)

DBI and DBI-2 are MIPI Alliance specifications for parallel interfaces to display modules having display controllers and frame buffers. For systems based on these specifications, the host processor loads images to the on-panel frame buffer through the display processor. Once loaded, the display controller manages all display refresh functions on the display module without further intervention from the host processor. Image updates require the host processor to write new data into the frame buffer.

300 DBI and DBI-2 specify a parallel interface; that is, data is sent to the peripheral over an 8-, 9- or 16-bit-301 wide parallel data bus, with additional control signals.

The DSI specification supports a Command Mode of operation. Like the parallel DBI, a DSI-compliant interface sends commands and parameters to the display. However, all information in DSI is first serialized before transmission to the display module. <u>At the display, serial information is transformed back to parallel</u> data and control signals for the on-panel display controller. Similarly, the display module can return status information and requested memory data to the host processor, using the same serial data path.

### 307 3.2 DPI and DPI-2 (Display Pixel Interface Standards for Parallel Signaling)

308 DPI and DPI-2 are MIPI Alliance specifications for parallel interfaces to display modules without on-panel 309 display controller or frame buffer. These display modules rely on a steady flow of pixel data from host 310 processor to the display, to maintain an image without flicker or other visual artifacts. MIPI Alliance 311 specifications document several pixel formats for *Active Matrix* (AM) display modules.

312 Like DBI and DBI-2, DPI and DPI-2 are specifications for parallel interfaces. The data path may be 16-,

313 18-, or 24-bits wide, depending on pixel format(s) supported by the display module. This specification 314 refers to DPI mode of operation as Video Mode.

Some display modules that use Video Mode in normal operation also make use of a simplified form of Command Mode, when in low-power state. These display modules can shut down the streaming video interface and continue to refresh the screen from a small local frame buffer, at reduced resolution and pixel depth. The local frame buffer shall be loaded, prior to interface shutdown, with image content to be displayed when in low-power operation. These display modules can switch mode in response to powercontrol commands.

### 321 **3.3 DCS (Display Command Set)**

DCS is a specification for the command set used by DSI and DBI-2 specifications. Commands are sent from the host processor to the display module. On the display module, a display controller receives and interprets commands, then takes appropriate action. Commands fall into four broad categories: read register, write register, read memory and write memory. A command may be accompanied by multiple parameters.

### 327 3.4 CSI-2 (Camera Serial Interface 2)

328 CSI-2 is a MIPI Alliance standard for serial interface between a camera module and host processor. It is

329 based on the same physical layer technology and low-level protocols as DSI. Some significant differences

330 are:

- CSI-2 uses unidirectional high-speed Link, whereas DSI is half-duplex bidirectional Link

- CSI-2 makes use of a secondary channel, based on I<sup>2</sup>C, for control and status functions

CSI-2 data direction is from peripheral (Camera Module) to host processor, while DSI's primary data

direction is from host processor to peripheral (Display Module).

### 335 **3.5 D-PHY (MIPI Alliance Standard for Physical Layer)**

*MIPI Alliance Standard for D-PHY* [4] provides the physical layer definition for DSI. The functionality specified by the D-PHY standard covers all electrical and timing aspects, as well as low-level protocols, signaling, and message transmissions in various operating modes.

### **339 4 DSI Introduction**

DSI specifies the interface between a host processor and a peripheral such as a display module. It builds on

existing MIPI Alliance standards by adopting pixel formats and command set specified in DPI-2, DBI-2

and DCS standards.

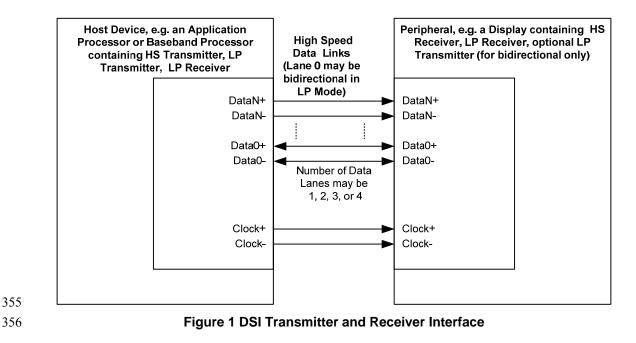

Figure 1 shows a simplified DSI interface. From a conceptual viewpoint, a DSI-compliant interface performs the same functions as interfaces based on DBI-2 and DPI-2 standards or similar parallel display interfaces. It sends pixels or commands to the peripheral, and can read back status or pixel information from the peripheral. The main difference is that DSI serializes all pixel data, commands, and events that, in traditional or legacy interfaces, are normally conveyed to and from the peripheral on a parallel data bus with additional control signals.

From a system or software point of view, the serialization and deserialization operations should be transparent. The most visible, and unavoidable, consequence of transformation to serial data and back to parallel is increased latency for transactions that require a response from the peripheral. For example, reading a pixel from the frame buffer on a display module will have a higher latency using DSI than DBI. Another fundamental difference is the host processor's inability during a read transaction to throttle the rate, or size, of returned data.

Peripheral

#### 357 4.1 **DSI Layer Definitions**

### **Application Processor**

358

359

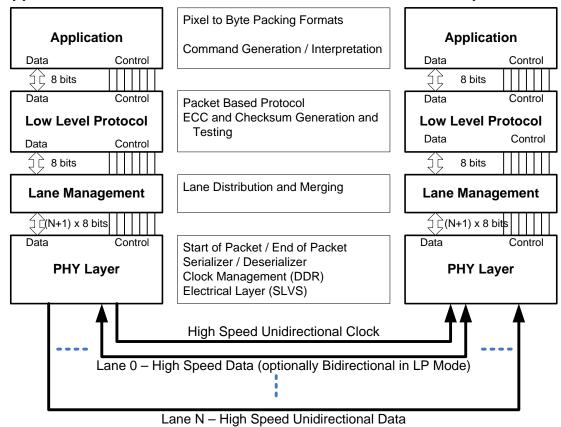

### Figure 2 DSI Layers

360 A conceptual view of DSI organizes the interface into several functional layers. A description of the layers follows and is also shown in Figure 2. 361

362 **PHY Layer:** The *PHY Layer* specifies transmission medium (electrical conductors), the input/output 363 circuitry and the clocking mechanism that captures "ones" and "zeroes" from the serial bit stream. This part of the specification documents the characteristics of the transmission medium, electrical parameters for 364 365 signaling and the timing relationship between clock and Data Lanes.

366 The mechanism for signaling Start of Transmission (SoT) and End of Transmission (EoT) is specified, as well as other "out of band" information that can be conveyed between transmitting and receiving PHYs. 367 Bit-level and byte-level synchronization mechanisms are included as part of the PHY. Note that the 368 369 electrical basis for DSI (SLVS) has two distinct modes of operation, each with its own set of electrical 370 parameters.

371 The PHY layer is described in MIPI Alliance Standard for D-PHY [4].

372 Lane Management Layer: DSI is Lane-scalable for increased performance. The number of data signals 373 may be 1, 2, 3, or 4 depending on the bandwidth requirements of the application. The transmitter side of the 374 interface distributes the outgoing data stream to one or more Lanes ("distributor" function). On the 375 receiving end, the interface collects bytes from the Lanes and merges them together into a recombined data 376 stream that restores the original stream sequence ("merger" function).

377 Protocol Layer: At the lowest level, DSI protocol specifies the sequence and value of bits and bytes 378 traversing the interface. It specifies how bytes are organized into defined groups called packets. The 379 protocol defines required headers for each packet, and how header information is generated and interpreted. 380 The transmitting side of the interface appends header and error-checking information to data being 381 transmitted. On the receiving side, the header is stripped off and interpreted by corresponding logic in the 382 receiver. Error-checking information may be used to test the integrity of incoming data. DSI protocol also 383 documents how packets may be tagged for interleaving multiple command or data streams to separate 384 destinations using a single DSI.

Application Layer: This layer describes higher-level encoding and interpretation of data contained in the data stream. Depending on the display subsystem architecture, it may consist of pixels having a prescribed format, or of commands that are interpreted by the display controller inside a display module. The DSI specification describes the mapping of pixel values, commands and command parameters to bytes in the packet assembly. See *MIPI Alliance Standard for Display Command Set* [1].

### **390 4.2 Command and Video Modes**

DSI-compliant peripherals support either of two basic modes of operation: Command Mode and Video

Mode. Which mode is used depends on the architecture and capabilities of the peripheral. The mode

definitions reflect the primary intended use of DSI for display interconnect, but are not intended to restrict

DSI from operating in other applications.

Typically, a peripheral is capable of Command Mode operation or Video Mode operation. Some Video Mode displays also include a simplified form of Command Mode operation in which the display may refresh its screen from a reduced-size, or partial, frame buffer, and the interface (DSI) to the host processor may be shut down to reduce power consumption.

### 399 4.2.1 Command Mode

400 Command Mode refers to operation in which transactions primarily take the form of sending commands 401 and data to a peripheral, such as a display module, that incorporates a display controller. The display 402 controller may include local registers and a frame buffer. Systems using Command Mode write to, and read 403 from, the registers and frame buffer memory. The host processor indirectly controls activity at the 404 peripheral by sending commands, parameters and data to the display controller. The host processor can also 405 read display module status information or the contents of the frame memory. Command Mode operation 406 requires a bidirectional interface.

#### 407 **4.2.2** Video Mode Operation

Video Mode refers to operation in which transfers from the host processor to the peripheral take the form of a real-time pixel stream. In normal operation, the display module relies on the host processor to provide image data at sufficient bandwidth to avoid flicker or other visible artifacts in the displayed image. Video information should only be transmitted using High Speed Mode.

412 Some Video Mode architectures may include a simple timing controller and partial frame buffer, used to 413 maintain a partial-screen or lower-resolution image in standby or low-power mode. This permits the 414 interface to be shut down to reduce power consumption.

To reduce complexity and cost, systems that only operate in Video Mode may use a <u>unidirectional</u> data path.

#### 417 **4.2.3 Virtual Channel Capability**

418 While this specification only addresses the connection of a host processor to a single peripheral, DSI 419 incorporates a virtual channel capability for communication between a host processor and multiple, 420 physical display modules. Display modules are completely independent, may operate simultaneously, and 421 may be of different display architecture types, limited only by the total bandwidth available over the shared 422 DSI Link. The details of connecting multiple peripherals to a single Link are beyond the scope of this 423 document.

Since interface bandwidth is shared between peripherals, there are constraints that limit the physical extent and performance of multiple-peripheral systems.

The DSI protocol permits up to four virtual channels, enabling traffic for multiple peripherals to share a common DSI Link. In some high-resolution display designs, multiple physical drivers serve different areas of a common display panel. Each driver is integrated with its own display controller that connects to the host processor through DSI. Using virtual channels, the display controller directs data to the individual drivers, eliminating the need for multiple interfaces or complex multiplexing schemes.

## 431 **5 DSI Physical Layer**

This section provides a brief overview of the physical layer used in DSI. See *MIPI Alliance Standard for D-PHY* [4] for more details.

Information is transferred between host processor and peripheral using one or more serial data signals and

accompanying serial clock. The action of sending high-speed serial data across the bus is called a *HS transmission* or *burst*.

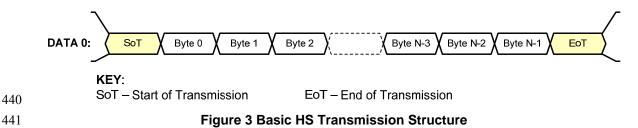

- 437 Between transmissions, the differential data signal or Lane goes to a low-power state (LPS). Interfaces

- 438 should be in LPS when they are not actively transmitting or receiving high-speed data. Figure 3 shows the

- 439 basic structure of a HS transmission. *N* is the total number of bytes sent in the transmission.

442 D-PHY low-level protocol specifies a minimum data unit of one byte, and a transmission contains an 443 integer number of bytes.

### 444 **5.1 Data Flow Control**

There is no handshake between the Protocol and PHY layers that permit the Protocol layer to throttle data transfer to, or from, the PHY layer once transmission is underway. Packets shall be sent and received in their entirety and without interruption. The Protocol layer and data buffering on both ends of the Link shall always have bandwidth equal to, or greater than, PHY layer circuitry. A practical consequence is that the system implementer should ensure that receivers have bandwidth capability that is equal to, or greater than, that of the transmitter.

### 451 **5.2 Bidirectionality and Low Power Signaling Policy**

The physical layer for a DSI implementation is composed of one to four Data Lanes and one Clock Lane. In a Command Mode system, Data Lane 0 shall be bidirectional; additional Data Lanes shall be unidirectional. In a Video Mode system, Data Lane 0 may be bidirectional or unidirectional; additional Data Lanes shall be unidirectional. See sections 5.3 and 5.4 for details.

- 456 For both interface types, the Clock Lane shall be driven by the host processor only, never by the peripheral.

- 457 Forward direction Low Power transmissions shall use Data Lane 0 only. Reverse direction transmissions on

- 458 Data Lane 0 shall use Low Power Mode only. The peripheral shall be capable of receiving any transmission

- 459 in Low Power or High Speed Mode. Note that transmission bandwidth is substantially reduced when

- 460 transmitting in LP mode.

- 461 For bidirectional Lanes, data shall be transmitted in the peripheral-to-processor, or reverse, direction using

- 462 Low-Power (LP) Mode only. See MIPI Alliance Standard for D-PHY [4] for details on the different modes

- 463 of transmission.

- 464 The interface between PHY and Protocol layers has several signals controlling bus direction. When a host

- transmitter requires a response from a peripheral, e.g. returning READ data or status information, it asserts TurnRequest to its PHY during the last packet of the transmission. This tells the PHY layer to assert the

- 467 Bus Turn-Around (BTA) command following the EoT sequence.

When a peripheral receives the Bus Turn-Around command, its PHY layer asserts TurnRequest as an input to the Protocol layer. This tells the receiving Protocol layer that it shall prepare to send a response to the host processor. Normally, the packet just received will tell the Protocol layer what information to send once the bus is available for transmitting to the host processor.

472 After transmitting its response, the peripheral similarly hands bus control back to the host processor using a 473 TurnRequest to its own PHY layer.

### 474 **5.3 Command Mode Interfaces**

- 475 The minimum physical layer requirement for a DSI host processor operating in Command Mode is:

- Data Lane Module: CIL-MUYY (HS-TX, LP-TX, LP-RX, and LP-CD)

- Clock Lane Module: CIL-MCNN (HS-TX, LP-TX)

- 478 The minimum physical layer requirement for a DSI peripheral operating in Command Mode is:

- Data Lane Module: CIL-SUYY (HS-RX, LP-RX, LP-TX, and LP-CD)

- 480 Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

- 481 Bidirectional Links shall support reverse-direction Escape Mode as well as forward direction Escape Mode.

#### 482 **5.4 Video Mode Interfaces**

- 483 The minimum physical layer requirement for a DSI transmitter operating in Video Mode is:

- Data Lane Module: CIL-MUNN (HS-TX, LP-TX)

- 485 Clock Lane Module: CIL-MCNN (HS-TX, LP-TX)

- 486 The minimum physical layer requirement for a DSI receiver operating in Video Mode is:

- Data Lane Module: CIL-SUNN (HS-RX, LP-RX)

- 488 Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

- 489 All DSI implementations should support forward escape ULPM on all Data Lanes.

#### 490 **5.5 Bidirectional Control Mechanism**

Turning the bus around is controlled by a token-passing mechanism: the host processor sends a Bus Turn-Around (BTA) request, which conveys to the peripheral its intention to release, or stop driving, the data path after which the peripheral can transmit one or more packets back to the host processor. When it is finished, the peripheral shall return control of the bus back to the host processor. Bus Turn-Around is signaled using an Escape Mode mechanism provided by PHY-level protocol.

- 496 In bidirectional systems, there is a remote chance of erroneous behavior due to EMI that could result in bus

- 497 contention. Mechanisms are provided in this specification for recovering from any bus contention event498 without forcing "hard reset" of the entire system.

### 499 **5.6 Clock Management**

- 500 DSI Clock is a signal from the host processor to the peripheral. In some systems, it may serve multiple 501 functions:

- 502 **DSI Bit Clock:** Across the Link, DSI Clock is used as the source-synchronous bit clock for capturing serial data bits in the receiver PHY. This clock shall be active while data is being transferred.

504 **Byte Clock:** Divided down, DSI Clock is used to generate a byte clock at the conceptual interface between 505 the Protocol and Application layers. During HS transmission, each byte of data is accompanied by a byte 506 clock. Like the DSI Bit Clock, the byte clock shall be active while data is being transferred. At the Protocol 507 layer to Application layer interface, all actions are synchronized to the byte clock.

508 Application Clock(s): Divided-down versions of DSI Bit Clock may be used for other clocked functions at 509 the peripheral. These "application clocks" may need to run at times when no serial data is being transferred, 510 or they may need to run constantly (continuous clock) to support active circuitry at the peripheral. Details 511 of how such additional clocks are generated and used are beyond the scope of this specification.

For continuous clock behavior, the Clock Lane remains in high-speed mode generating active clock signals

between HS data packet transmissions. For non-continuous clock behavior, the Clock Lane enters the LP-

514 11 state between HS data packet transmissions.

### 515 **5.6.1 Clock Requirements**

All DSI transmitters and receivers shall support continuous clock behavior on the Clock Lane, and optionally may support non-continuous clock behavior. A DSI host processor shall support continuous clock for systems that require it, as well as having the capability of shutting down the serial clock to reduce power.

520 Note that the host processor controls the desired mode of clock operation. Host protocol and applications 521 control Clock Lane operating mode (High Speed or Low Power mode). System designers are responsible 522 for understanding the clock requirements for peripherals attached to DSI and controlling clock behavior in 523 accordance with those requirements.

Note that in Low Power signaling mode, LP clock is functionally embedded in the data signals. When LP data transmission ends, the clock effectively stops and subsequent LP clocks are not available to the peripheral. If the peripheral requires additional clocks to advance the state of its logic, to move date through sequential buffers, or similar, it may be necessary to add 'dummy' data bytes to the LP transmission to effect forward progress of state machines or to advance data through sequential logic.

The handshake process for BTA allows only limited mismatch of Escape Mode clock frequencies between a host processor and a peripheral. The Escape Mode frequency ratio between host processor and peripheral shall not exceed 3:2. The host processor is responsible for controlling its own clock frequency to match the peripheral. The host processor LP clock frequency shall be in the range of 67% to 150% of peripheral LP clock frequency. Therefore, the peripheral implementer shall specify a peripheral's nominal LP clock frequency and the guaranteed accuracy.

### 535 **5.6.2 Clock Power and Timing**

536 Additional timing requirements in MIPI Alliance Standard for D-PHY [4] specify the timing relationship

between the power state of data signal(s) and the power state of the clock signal. It is the responsibility of the host processor to observe this timing relationship. If the DSI Clock runs continuously, these timing

539 requirements do not apply.

### 540 6 Multi-Lane Distribution and Merging

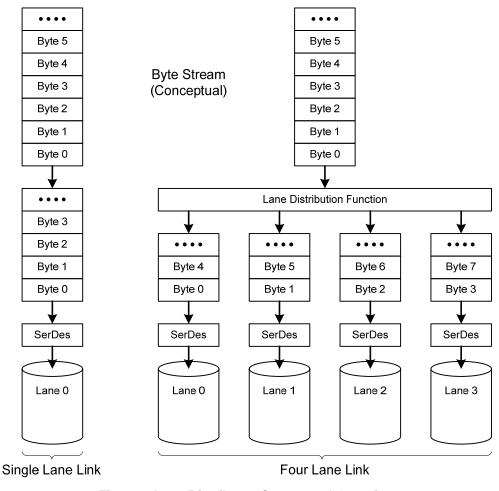

541 DSI is a Lane-scalable specification. Applications requiring more bandwidth than that provided by one 542 Data Lane may expand the data path to two, three, or four Lanes wide and obtain approximately linear 543 increases in peak bus bandwidth. This specification explicitly documents the mapping between application 544 data and the serial bit stream to ensure compatibility between host processors and peripherals that make use 545 of multiple Lanes.

546 Multi-Lane implementations shall use a single common clock signal, shared by all Data Lanes.

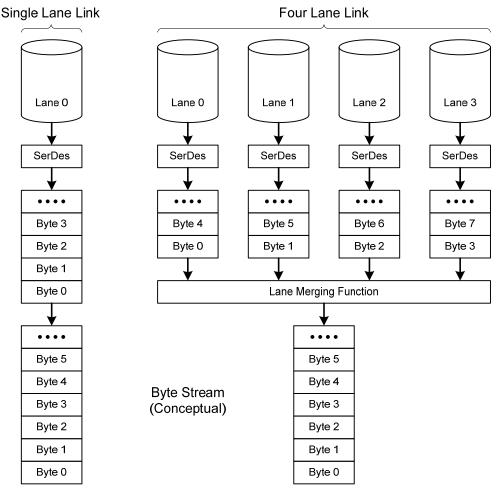

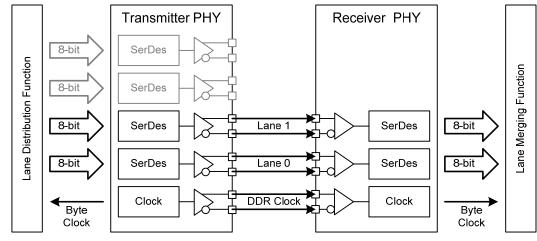

547 Conceptually, between the PHY and higher functional blocks is a layer that enables multi-Lane operation. 548 In the transmitter, shown in Figure 4, this layer distributes a sequence of packet bytes across N Lanes, 549 where each Lane is an independent block of logic and interface circuitry. In the receiver, shown in Figure 5, 550 the layer collects incoming bytes from N Lanes and consolidates the bytes into complete packets to pass 551 into the following packet decomposer.

552 553

Figure 4 Lane Distributor Conceptual Overview

Figure 5 Lane Merger Conceptual Overview

The Lane Distributor takes a HS transmission of arbitrary byte length, buffers N bytes, where N is the number of Lanes implemented in the interface, and sends groups of N bytes in parallel across the N Lanes. Before sending data, all Lanes perform the SoT sequence in parallel to indicate to their corresponding receiving units that the first byte of a packet is beginning. After SoT, the Lanes send groups of N bytes from the first packet in parallel, following a round-robin process. For example, with a two Lane system, byte 0 of the packet goes to Lane 0, byte 1 goes to Lane 1, byte 2 to Lane 0, byte 3 to Lane 1 and so on.

### 562 6.1 Multi-Lane Interoperability and Lane-number Mismatch

563 The number of Lanes used shall be a static parameter. It shall be fixed at the time of system design or initial 564 configuration and may not change dynamically. Typically, the peripheral's bandwidth requirement and its 565 corresponding Lane configuration establishes the number of Lanes used in a system.

566 The host processor shall be configured to support the same number of Lanes required by the peripheral. 567 Specifically, a host processor with N-Lane capability (N > 1) shall be capable of operation using fewer 568 Lanes, to ensure interoperability with peripherals having M Lanes, where N > M.

### Figure 6 Four-Lane Transmitter with Two-Lane Receiver Example

### 571 6.1.1 Clock Considerations with Multi-Lane

At EoT, the Protocol layer shall base its control of the common DSI Clock signal on the timing requirements for the last active Lane Module. If the Protocol layer puts the DSI Clock into LPS between HS transmissions to save power, it shall respect the timing requirement for DSI Clock relative to all serial data signals during the EoT sequence.

576 Prior to SoT, timing requirements for DSI Clock startup relative to all serial data signals shall similarly be 577 respected.

### 578 6.1.2 Bi-directionality and Multi-Lane Capability

Peripherals typically do not have substantial bandwidth requirements for returning data to the host

processor. To keep designs simple and improve interoperability, all DSI-compliant systems shall only use

Lane 0 in LP Mode for returning data from a peripheral to the host processor.

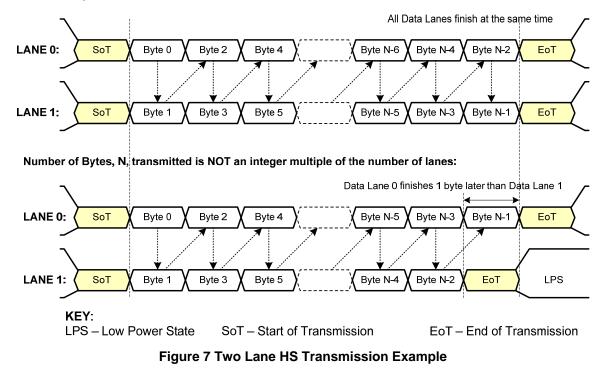

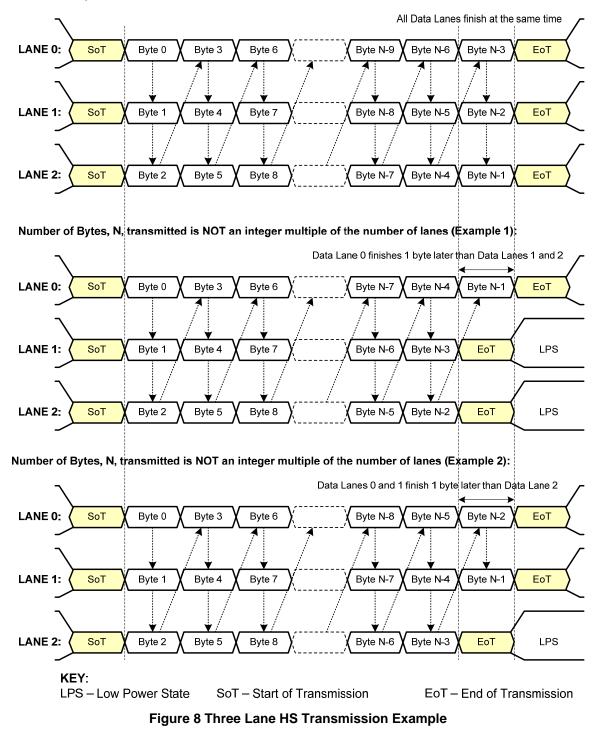

### 582 6.1.3 SoT and EoT in Multi-Lane Configurations

583 Since a HS transmission is composed of an arbitrary number of bytes that may not be an integer multiple of 584 the number of Lanes, some Lanes may run out of data before others. Therefore, the Lane Management 585 layer, as it buffers up the final set of less-than-N bytes, de-asserts its "valid data" signal into all Lanes for 586 which there is no further data.

587 Although all Lanes start simultaneously with parallel SoTs, each Lane operates independently and may 588 complete the HS transmission before the other Lanes, sending an EoT one cycle (byte) earlier.

589 The N PHYs on the receiving end of the Link collect bytes in parallel and feed them into the Lane 590 Management layer. The Lane Management layer reconstructs the original sequence of bytes in the 591 transmission.

Figure 7 and Figure 8 illustrate a variety of ways a HS transmission can terminate for different number ofLanes and packet lengths.

Note the special case of a multi-Lane implementation, having N Lanes, which may occasionally send a short, HS transmission where the packet length is less than N. In this case, Lanes without data to transmit shall remain in LPS.

#### Number of Bytes, N, transmitted is an integer multiple of the number of lanes:

600

#### Number of Bytes, N, transmitted is an integer multiple of the number of lanes:

## 601 **7** Low-Level Protocol Errors and Contention

For DSI systems there is a possibility that EMI, ESD or other transient-error mechanisms might cause one end of the Link to go to an erroneous state, or for the Link to transmit corrupted data.

In some cases, a transient error in a state machine, or in a clock or data signal, may result in detectable lowlevel protocol errors that indicate associated data is, or is likely to be, corrupt. Mechanisms for detecting and responding to such errors are detailed in the following sections.

- In other cases, a bidirectional PHY that should be receiving data could begin transmitting while the authorized transmitter is simultaneously driving the same data line, causing contention and lost data.

- 609 This section documents the minimum required functionality for recovering from certain low-level protocol 610 errors and contention. Low-level protocol errors are detected by logic in the PHY, while contention 611 problems are resolved using contention detectors and timers. Actual contention in DSI-based systems will 612 be very rare. In most cases, the appropriate use of timers will enable recovery from a transient contention 613 situation.

- Note that contention-related features are of no benefit for unidirectional DSI Links. However, the "common

mode fault" can still occur in unidirectional systems.

- 616 The following sections specify the minimum required functionality for detection of low-level protocol 617 errors, for contention recovery, and associated timers for host processors and peripherals using DSI.

### 618 **7.1 Low-Level Protocol Errors**

- Logic in the PHY can detect some classes of low-level protocol errors. These errors shall be communicated

to the Protocol layer via the PHY-Protocol Interface. The following errors shall be identified and stored by

the peripheral as status bits for later reporting to the host processor:

- 622 SoT Error

- 623 SoT Sync Error

- EoT Sync Error

- Escape Mode Entry Command Error

- LP Transmission Sync Error

- False Control Error

The mechanism for reporting and clearing these error bits is detailed in section 8.10.7. Note that unidirectional DSI peripherals are exempt from the reporting requirement since they cannot report such errors to the host processor.

#### 631 **7.1.1 SoT Error**

632 The leader sequence for Start of High-Speed Transmission (SoT) is fault tolerant for any single-bit error 633 and some multi-bit errors. The received synchronization bits and following data packet might therefore still 634 be uncorrupted if an error is detected, but confidence in the integrity of payload data will be lower. This 635 condition shall be communicated to the protocol with *SoT Error* flag.

### Table 1 Sequence of Events to Resolve SoT Error (HS RX Side)

| РНҮ                               | Protocol                                                                                                  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Detect SoT Error                  |                                                                                                           |  |

| Assert SoT Error flag to protocol | Receive and store SoT Error flag                                                                          |  |

|                                   | Send <i>SoT Error</i> in ACK packet, if requested; take no other action based on received HS transmission |  |

637 *SoT Error* is detected by the peripheral PHY. If an acknowledge response is expected, the peripheral shall 638 send a response using Data Type 02h (*Acknowledge with Error Report*) and set the *SoT Error* bit in the 639 return packet to the host processor. The peripheral should take no other action based on the potentially 640 corrupted received HS transmission.

### 641 **7.1.2 SoT Sync Error**

642 If the SoT leader sequence is corrupted in a way that proper synchronization cannot be expected, *SoT Sync* 643 *Error* shall be flagged. Subsequent data in the HS transmission is probably corrupt and should not be used.

644

### Table 2 Sequence of Events to Resolve SoT Sync Error (HS RX Side)

| РНУ                                                     | Protocol                                                                                                     |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Detect SoT Sync Error                                   |                                                                                                              |

| Assert SoT Sync Error to protocol                       | Receive and store SoT Sync Error flag                                                                        |

| May choose not to pass corrupted data to Protocol layer | Send <i>SoT Sync Error</i> with ACK packet if requested; take no other action based on received transmission |

645 *SoT Sync Error* is detected by the peripheral PHY. If an acknowledge response is expected, the peripheral 646 shall send a response using Data Type 02h (*Acknowledge with Error Report*) and set the *SoT Sync Error* bit 647 in the return packet to the host processor. Since data is probably corrupted, no command shall be 648 interpreted or acted upon in the peripheral. No WRITE activity shall be undertaken in the peripheral.

### 649 **7.1.3 EoT Sync Error**

DSI is a byte-oriented protocol. All uncorrupted HS transmissions contain an integer number of bytes. If, during EoT sequence, the peripheral PHY detects that the last byte does not match a byte boundary, *EoT Sync Error* shall be flagged. If an *Acknowledge* response is expected, the peripheral shall send *Acknowledge with Error Report*. The peripheral shall set the *EoT Sync Error* bit in the Error Report bytes of the return packet to the host processor.

If possible, the peripheral should take no action, especially WRITE activity, in response to the intended command. Since this error is not recognized until the end of the packet, some irreversible actions may take place before the error is detected.

#### Table 3 Sequence of Events to Resolve EoT Sync Error (HS RX Side)

| Receiving PHY                     | Receiving Protocol                                                                                            |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------|

| Detect EoT Sync Error             |                                                                                                               |

| Notify Protocol of EoT Sync Error | Receive and store EoT Sync Error flag                                                                         |

|                                   | Ignore HS transmission if possible; assert <i>EoT Sync</i><br><i>Error</i> if <i>Acknowledge</i> is requested |

### 659 **7.1.4 Escape Mode Entry Command Error**

660 If the Link begins an Escape Mode sequence, but the Escape Mode Entry command is not recognized by 661 the receiving PHY Lane, the receiver shall flag *Escape Mode Entry Command* error. This scenario could be 662 a legitimate command, from the transmitter point of view, that's not recognized or understood by the 663 receiving protocol. In bidirectional systems, receivers in both ends of the Link shall detect and flag 664 unrecognized Escape Mode sequences. Only the peripheral reports this error.

### 665 **Table 4 Sequence of Events to Resolve Escape Mode Entry Command Error (RX Side)**

| Receiving PHY                                                | Receiving Protocol                           |

|--------------------------------------------------------------|----------------------------------------------|

| Detect Escape Mode Entry Command error                       |                                              |

| Notify Protocol of <i>Escape Mode Entry Command</i><br>Error | Observe Escape Mode Entry Command Error flag |

| Go to Escape Wait until Stop state is observed               | Ignore Escape Mode transmission (if any)     |

| Observe Stop state                                           |                                              |

| Return to LP-RX Control mode                                 | set Escape Mode Entry Command Error bit      |

#### 666 **7.1.5 LP Transmission Sync Error**

667 This error flag is asserted if received data is not synchronized to a byte boundary at the end of Low-Power 668 Transmission. In bidirectional systems, receivers in both ends of the Link shall detect and flag LP 669 Transmission Sync errors. Only the peripheral reports this error.

670

### Table 5 Sequence of Events to Resolve LP Transmission Sync Error (RX Side)

| Receiving PHY                                             | Receiving Protocol                                                              |  |  |

|-----------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| Detect LP Transmission Sync Error                         |                                                                                 |  |  |

| Notify Protocol of LP Transmission Sync Error             | Receive LP Transmission Sync Error flag                                         |  |  |

| Return to LP-RX Control mode until Stop state is observed | Ignore Escape Mode transmission if possible, set appropriate error bit and wait |  |  |

#### 671 **7.1.6 False Control Error**

- 672 If a received LP-01 or LP-10 State is followed by a *Stop* state instead of the expected Turnaround or Escape

- Mode sequence, this error shall be flagged to the Protocol layer.

- 674

### Table 6 Sequence of Events to Resolve False Control Error (RX Side)

| Receiving PHY                                                                      | Receiving Protocol                                                          |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Detect False Control Error                                                         |                                                                             |

| Notify Protocol of False Control Error                                             | Observe <i>False Control</i> Error flag, set appropriate error bit and wait |

| Ignore Turnaround or Escape Mode request                                           |                                                                             |

| Remain in <i>LP-RECEIVE STATE Control</i> mode until <i>Stop</i> state is observed |                                                                             |

675 676

## Table 7 Low-Level Protocol Error Detection and Reporting

| Error Detected                     | HS Unidirectional, LP<br>Unidirectional, no Escape Mode |                   | HS Unidirectional, LP<br>Bidirectional with Escape Mode |                   |

|------------------------------------|---------------------------------------------------------|-------------------|---------------------------------------------------------|-------------------|

|                                    | Host Processor                                          | Peripheral        | Host Processor                                          | Peripheral        |

| SoT Error                          | NA                                                      | Detect, no report | NA                                                      | Detect and report |

| SoT Sync Error                     | NA                                                      | Detect, no report | NA                                                      | Detect and report |

| EoT Sync Error                     | NA                                                      | Detect, no report | NA                                                      | Detect and report |

| Escape Mode Entry<br>Command Error | No                                                      | No                | Detect and flag                                         | Detect and report |

| LP Transmission Sync Error         | No                                                      | No                | Detect and flag                                         | Detect and report |

| False Control Error                | No                                                      | No                | Detect and flag                                         | Detect and report |

### 677 **7.2 Contention Detection and Recovery**

678 Contention is a potentially serious problem that, although very rare, could cause the system to hang and 679 force a hard reset or power off / on cycle to recover. DSI specifies two mechanisms to minimize this 680 problem and enable easier recovery: contention detectors in the PHY for LP Mode contention, and timers 681 for other forms of contention and common-mode faults.

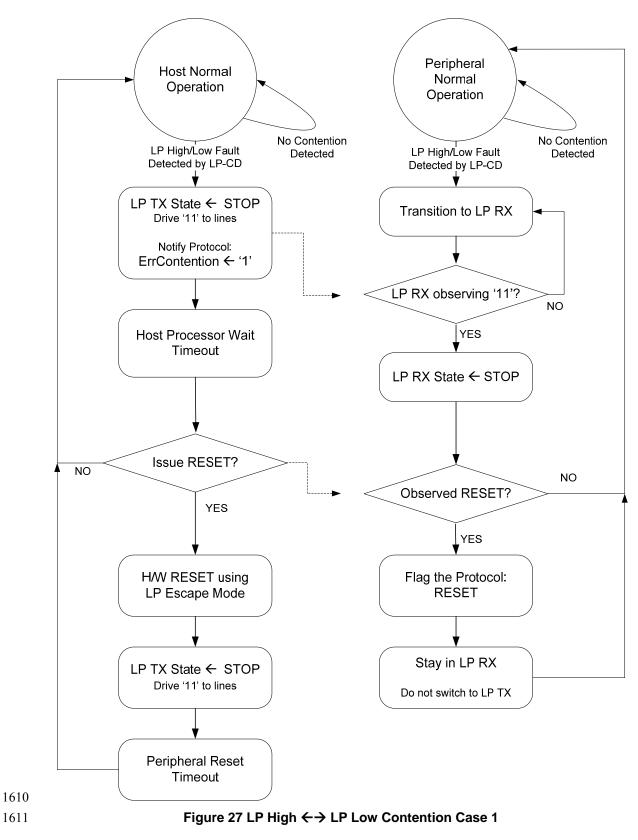

### 682 **7.2.1 Contention Detection in LP Mode**

- In bidirectional Links, contention detectors in the PHY shall detect two types of contention faults: LP High

Fault and LP Low Fault.

- 685 An LP High Fault occurs when a LP transmitter is driving high and the pin voltage is less than  $V_{IL}$ . An LP 686 Low Fault occurs when a LP transmitter is driving low and the pin voltage is greater than  $V_{ILF}$ .

Annex A provides detailed descriptions and state diagrams for PHY-based detection and recovery

procedures for LP contention faults. The state diagrams show a sequence of events beginning with

detection, and ending with return to normal operation.

### 690 **7.2.2 Contention Recovery Using Timers**

- The PHY cannot detect all forms of contention. Although they do not directly detect contention, the use of appropriate timers will ensure that any contention that does happen will be of limited duration.

- The time-out mechanisms described in this section are useful for recovering from contention failures, without forcing the system to undergo a hard reset (power off-on cycle).

#### 695 **7.2.2.1** Summary of Required Contention Recovery Timers

- Table 8 specifies the minimum required set of timers for contention recovery in a DSI system.

- 697

#### Table 8 Required Timers and Timeout Summary

| Timer                        | ner Timeout     |          | Requirement                          |

|------------------------------|-----------------|----------|--------------------------------------|

| HS RX Timer                  | HS RX Timeout   | HRX_TO   | <b>R</b> in bidirectional peripheral |

| HS TX Timer                  | HS TX Timeout   | HTX_TO   | <b>R</b> in host                     |

| LP TX Timer – Peripheral     | LP_TX-P Timeout | LTX-P_TO | <b>R</b> in bidirectional peripheral |

| LP RX Timer – Host Processor | LP_RX-H Timeout | LRX-H_TO | <b>R</b> in host                     |

#### 698 7.2.2.2 HS RX Timeout (HRX\_TO) in Peripheral

This timer is useful for recovering from some transient errors that may result in contention or commonmode fault. The HRX\_TO timer directly monitors the time a peripheral's HS receiver stays in High-Speed mode. It is programmed to be longer than the maximum duration of a High-Speed transmission expected by the peripheral receiver. HS RX timeout will signal an error during HS RX mode if EoT is not received before the timeout expires.

704 Combined with HTX\_TO, these timers ensure that a transient error will limit contention in HS mode to the

timeout period, and the bus will return to a normal LP state. The Timeout value is protocol specific. HS RX

- 706 Timeout shall be used for Bidirectional Links and for Unidirectional Links with Escape Mode. HS RX

- 707 Timeout is recommended for all DSI peripherals and required for all bidirectional DSI peripherals.

#### Table 9 Sequence of Events for HS RX Timeout (Peripheral initially HS RX)

| Host Processor Side                            | Peripheral Side                                                           |

|------------------------------------------------|---------------------------------------------------------------------------|

| Drives bus HS-TX                               | HS RX Timeout Timer Expires                                               |

|                                                | Transition to LP-RX                                                       |

| End HS transmission normally, or HS-TX timeout | Peripheral waits for <i>Stop</i> state before responding to bus activity. |

| Transition to Stop state (LP-11)               | Observe Stop state and flag error                                         |

709 During this mode, the HS clock is active and can be used for the HS RX Timer in the peripheral.

The LP High Fault and LP Low Fault are caused by both sides of the Link transmitting simultaneously.

Note, the LP High Fault and LP Low Fault are only applicable for bidirectional data lanes.

The Common Mode fault occurs when the transmitter and receiver are not in the same communication mode, e.g. transmitter (host processor) is driving LP-01 or LP-10, while the receiver (peripheral) is in HS-RX mode with terminator connected. There is no contention, but the receiver will not capture transmitted data correctly. This fault may occur in both bidirectional and unidirectional lanes. After HS RX timeout, the peripheral returns to LP-RX mode and normal operation may resume. Note that in the case of a common-mode fault, there may be no DSI serial clock from the host processor. Therefore, another clock source for HRX TO timer may be required.

### 719 7.2.2.3 HS TX Timeout (HTX\_TO) in Host Processor

This timer is used to monitor a host processor's own length of HS transmission. It is programmed to be longer than the expected maximum duration of a High-Speed transmission. The maximum HS transmission length is protocol-specific. If the timer expires, the processor forces a clean termination of HS transmission and enters EoT sequence, then drives LP-11 state. This timeout is required for all host processors.

#### 724 Table 10 Sequence of Events for HS TX Timeout (Host Processor initially HS TX)

| Host Processor Side                      | Peripheral Side                                       |

|------------------------------------------|-------------------------------------------------------|

| Host Processor in HS TX mode             | Peripheral in HS RX mode                              |

| HS TX Timeout Timer expires, forces EoT  |                                                       |

| Host Processor drives Stop state (LP-11) | Peripheral observes EoT and <i>Stop</i> state (LP-RX) |

### 725 7.2.2.4 LP TX-Peripheral Timeout (LTX-P\_TO)

This timer is used to monitor the peripheral's own length of LP transmission (bus possession time) when in

LP TX mode. The maximum transmission length in LP TX is determined by protocol and data formats. This timeout is useful for recovering from LP-contention. LP TX-Peripheral Timeout is required for bidirectional peripherals.

### Table 11 Sequence of Events for LP TX-Peripheral Timeout (Peripheral initially LP TX)

| Host Processor Side                      | Peripheral Side                                                           |

|------------------------------------------|---------------------------------------------------------------------------|

| (possible contention)                    | Peripheral in LP TX mode                                                  |

|                                          | LP TX-P Timeout Timer Expires                                             |

|                                          | Transition to LP-RX                                                       |

| Detect contention, or Host LP-RX Timeout | Peripheral waits for <i>Stop</i> state before responding to bus activity. |

| Drive LP-11 Stop state                   | Observe Stop state in LP-RX mode                                          |

731 Note that host processor LP-RX timeout (see 7.2.2.5) should be set to a *longer* value than the peripheral's

732 LP-TX-P timer, so that the peripheral has returned to LP-RX state and is ready for further commands

following receipt of LP-11 from the host processor. 733

#### 7.2.2.5 LP-RX Host Processor Timeout (LRX-H TO) 734

735 The LP-RX timeout period in the Host Processor shall be greater than the LP TX-Peripheral timeout. Since both timers begin counting at approximately the same time, this ensures the peripheral has returned to LP-736 RX mode and is waiting for bus activity (commands from Host Processor, etc.) when LP-RX timer expires 737 in the host. The timeout value is protocol specific. This timer is required for all Host Processors. 738

#### 739 Table 12 Sequence of Events for Host Processor Wait Timeout (Peripheral initially TX)

| Host Processor Side                      | Peripheral Side                              |

|------------------------------------------|----------------------------------------------|

| Host Processor in LP RX mode             | (peripheral LP-TX timeout)                   |

| Host Processor LP-RX Timer expires       | Peripheral waiting in LP-RX mode             |

| Host Processor drives Stop state (LP-11) | Peripheral observes Stop state in LP-RX mode |

#### 740 7.3 **Additional Timers**

741 Additional timers are used to detect bus turnaround problems and to ensure sufficient wait time after Reset 742 is sent to the peripheral.

#### 743 7.3.1 Turnaround Acknowledge Timeout (TA\_TO)

When either end of the Link issues BTA (Bus Turn-Around), its PHY shall monitor the sequence of data-744 lane states during the ensuing turnaround process. In a normal BTA sequence, the turnaround completes 745 within a bounded time, with the other end of the Link finally taking bus possession and driving LP-11 (Stop 746 state) on the bus. If the sequence is observed not to complete (by the previously-transmitting PHY) within 747 748 the specified time period, the timer TA TO times out and begins a recovery procedure or re-sends BTA. 749 This specified period shall be longer then the maximum possible turnaround delay for the unit to which the 750 turnaround request was sent. This is an optional timer.

751 752

| 1 | Table 13 Sequence of Events for Turnaround Acknowledge Timeout (Peripheral initially |

|---|--------------------------------------------------------------------------------------|

| 2 | TX)                                                                                  |

| Host Processor Side | Peripheral Side                    |

|---------------------|------------------------------------|

| Host in LP RX mode  | Peripheral in LP TX mode           |

|                     | Send Turnaround back to Host       |

| (no change)         | Turnaround Acknowledgement Timeout |

|                     | Transition to LP-RX                |

<sup>753</sup> 754

# Table 14 Sequence of Events for Turnaround Acknowledge Timeout (Host Processorinitially TX)

| Host Processor Side                   | Peripheral Side          |

|---------------------------------------|--------------------------|

| Host Processor in HS TX or LP TX mode | Peripheral in LP RX mode |

| Request Turnaround                    |                          |

| Turnaround Acknowledgement Timeout    | (no change)              |

| Return to <i>Stop</i> state (LP-11)   |                          |

### 755 7.3.2 Peripheral Reset Timeout (PR\_TO)

When a peripheral is reset, it requires a period of time before it is ready for normal operation. This timer is programmed with a value longer than the specified time required to complete the reset sequence. After it expires, the host may resume normal operation with the peripheral. The timeout value is peripheralspecific. This is an optional timer.

760

### Table 15 Sequence of Events for Peripheral Reset Timeout

| Host Processor Side          | Peripheral Side             |

|------------------------------|-----------------------------|

| Send Reset Entry command     | Receive Reset Entry Command |

| Return to Stop state (LP-11) | Initiate reset sequence     |

|                              | Complete reset sequence     |

| Peripheral Reset Timeout     |                             |

|                              |                             |

| Resume Normal Operation.     | Wait for bus activity       |

### 761 **7.4** Acknowledge and Error Reporting Mechanism

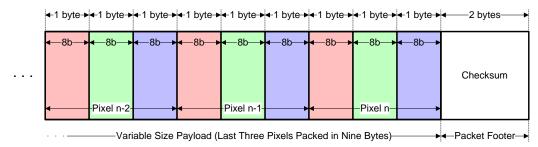

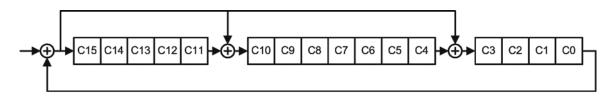

762 In a bidirectional Link, the peripheral monitors each transmission from the host processor, using detection