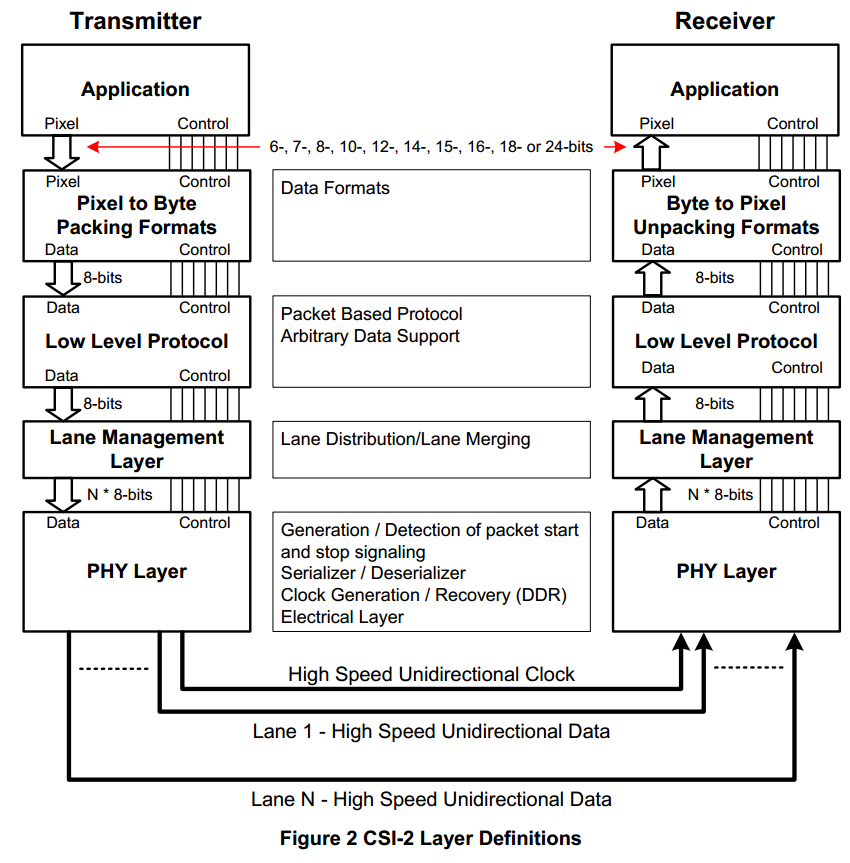

在前面的文章中介绍过D-PHY的分层结构图,而基于D-PHY的CSI-2协议主要定义的是Lane Management Layer、Low Level Protocol和像素与字节格式转换(Pixel to Byte和Byte to Pixel)部分。严格来说,可以将像素与字节转换层划分到应用层中去,但是考虑到MIPI CSI-2的应用场合相对固定,很多情况下像素与字节转换层都是由硬件来实现的(以获得更高的效率)。至于Lane Management Layer和Low Level Protocol则是DSI和CSI-2所共有的特性(基本上是一致的),所以也有的MIPI参考资料将这两层放在了D-PHY那部分进行了介绍。

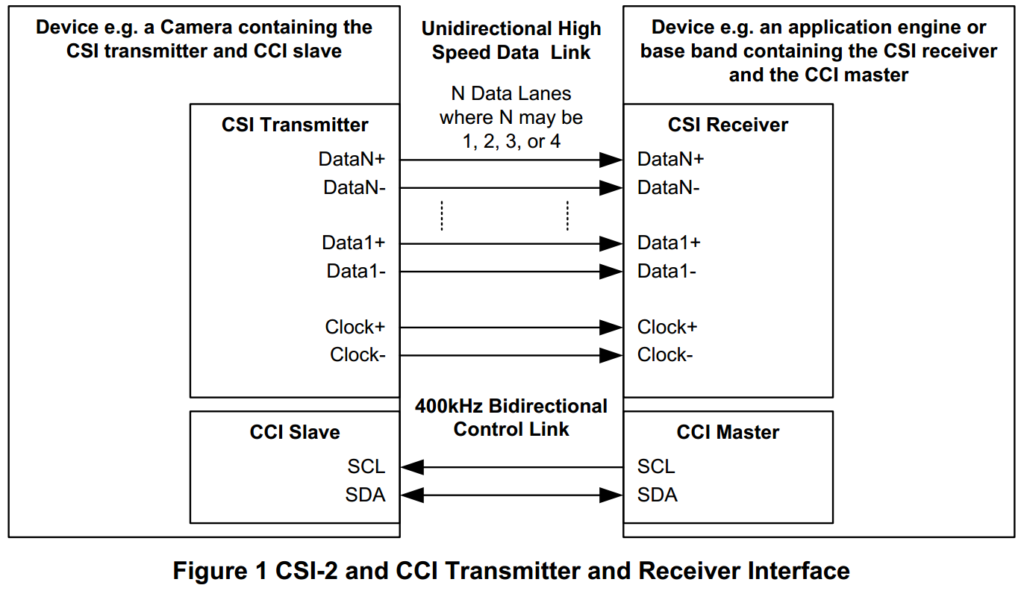

一个简化的CSI-2的接口模型如下图所示:

可以发现,CSI-2无论是Data Lane还是Clock Lane都是非双向的(Unidirectional),同时CSI-2协议还囊括了CCI(Camera Control Interface)协议。不过这也很容易理解,CSI-2定义的是摄像头和图像处理器或者应用处理器之间的接口协议,此时摄像头为Transmitter,而应用处理器为Receiver,只需要进行单向的图像数据传输即可了,而应用处理器可以通过CCI接口来对摄像头进行配置。为什么要用CCI呢?主要是为了保持良好的兼容性,因为CCI已经被行业所认可和接受,并被广泛应用于多家公司的产品中。

那么CCI又是什么鬼呢?你可以这么理解,它就是I2C的一个变种,或者说CCI是I2C协议的一个子集。因此,使用I2C接口就可以直接与CCI接口互联,以实现通信。

需要注意的是,在MIPI CSI-2的协议规范中明确的对摄像头的CCI地址做出了规定,具体如下:

对于那些只支持RAW Bayer输出格式的摄像头,其CCI地址必须为011011xb(x=0,1);对于其他的摄像头,其CCI地址必须为011110xb。

对于CCI协议的具体内容,这里就不详细介绍了,大家可以去参考I2C协议规范或者CSI-2协议规范的对应章节就可以了。

在前面介绍D-PHY的文章中有提到过,当系统进入LP模式时,Clock Lane上的差分时钟可以设置为关闭,或者继续运行。对于那些在LP模式下(换一种说法就是,在两次HS模式之间),差分时钟信号仍然有效的系统,称之为持续时钟行为(Continuous Clock Behavior);而对于那些在LP模式下,将差分时钟信号切断的系统,则称之为非持续时钟行为(Non-Continuous Clock Behavior)。

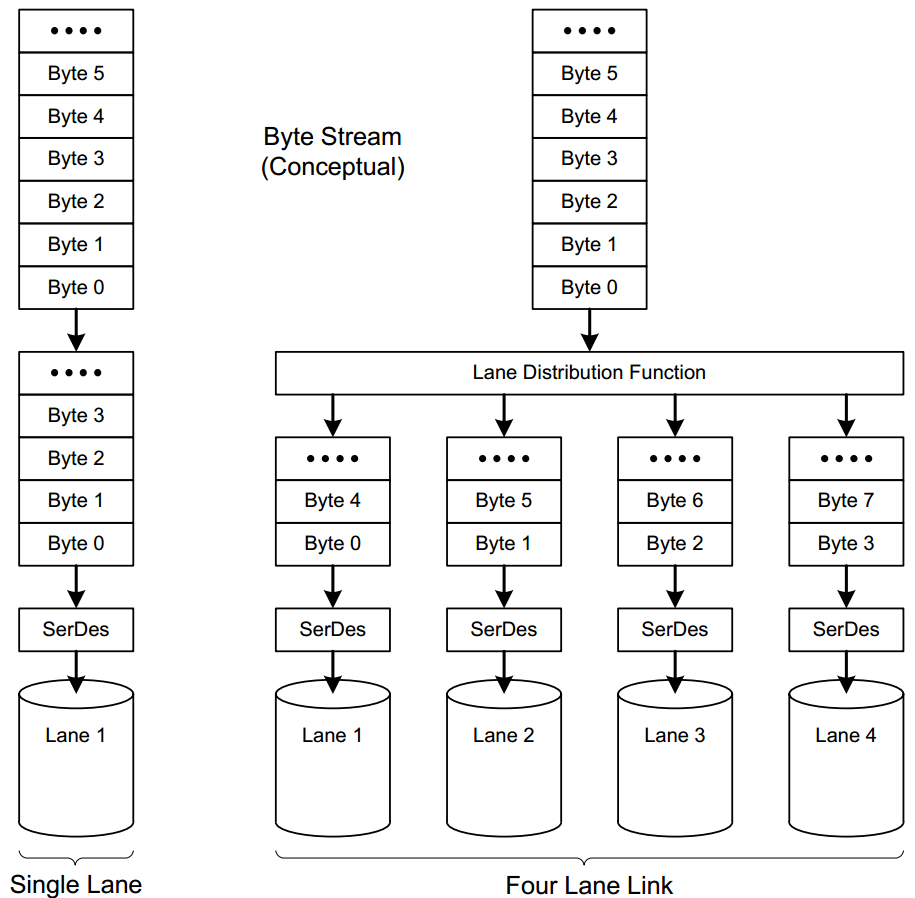

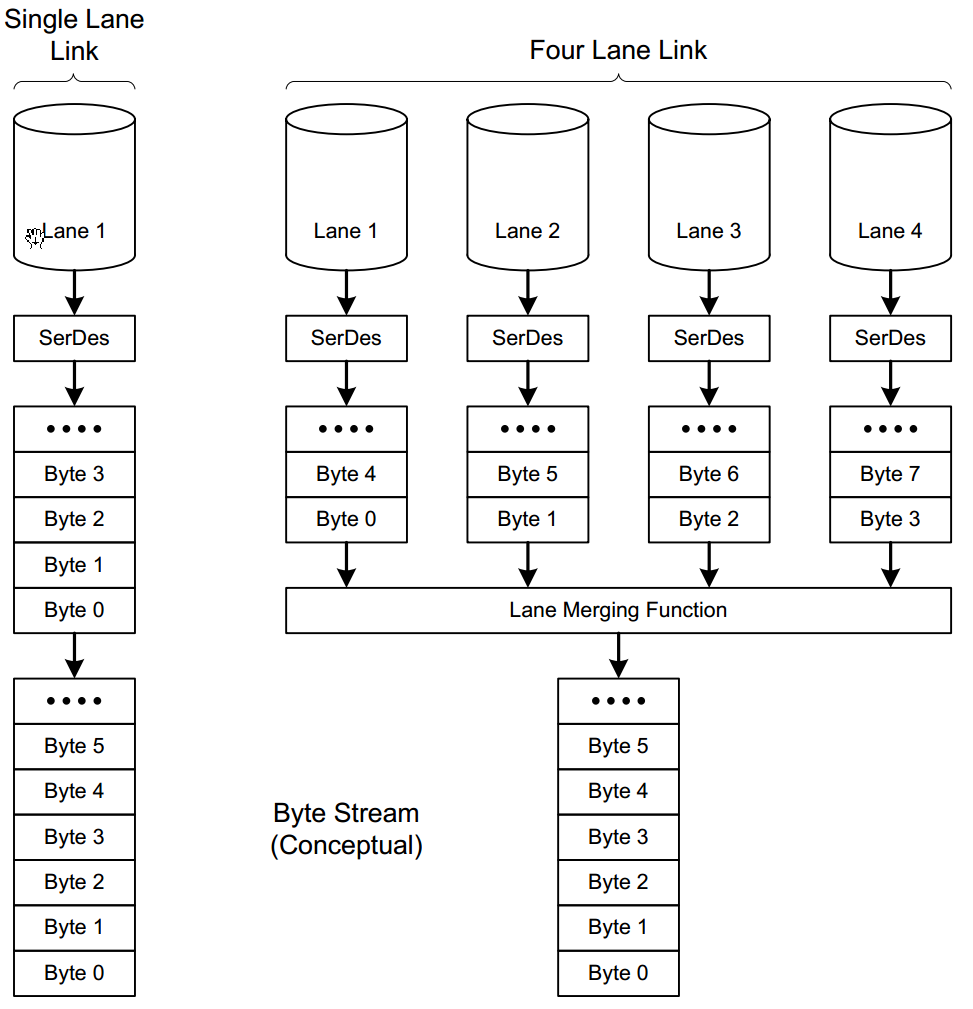

MIPI CSI-2协议支持多种Lane的配置方式,最小仅仅需要一个Clock Lane和一个Data Lane,而最大则支持一个Clock Lane和多大4个Data Lane。其中,4个Data Lane由Clock Lane进行同步传输数据,显然,这需要在传输数据之前对数据进行分配(或者合并),具体如下图所示:

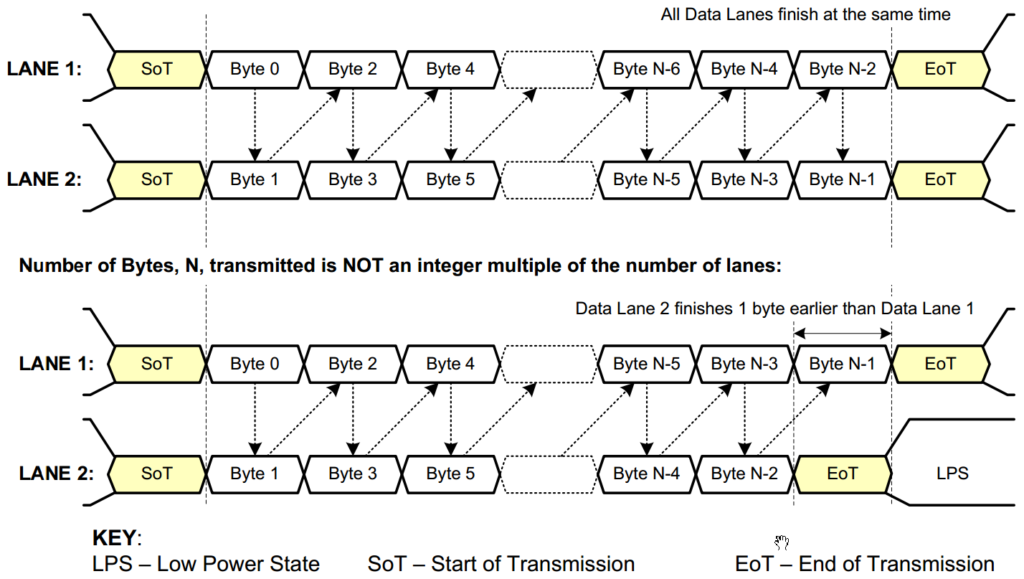

显然CSI-2每个Data Lane的最小传输内容为一个字节。同时,这会带来一个问题(以2个Data Lane)为例,当所传送字节数为偶数时,Lane1和Lane2可以同时结束,当所传送的字节数为奇数时,Lane1和Lane2将不再是同时结束了!具体如下图所示:

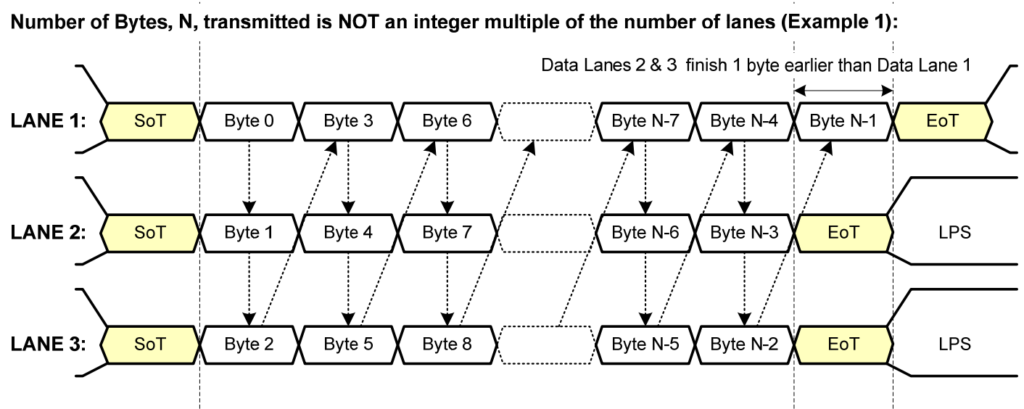

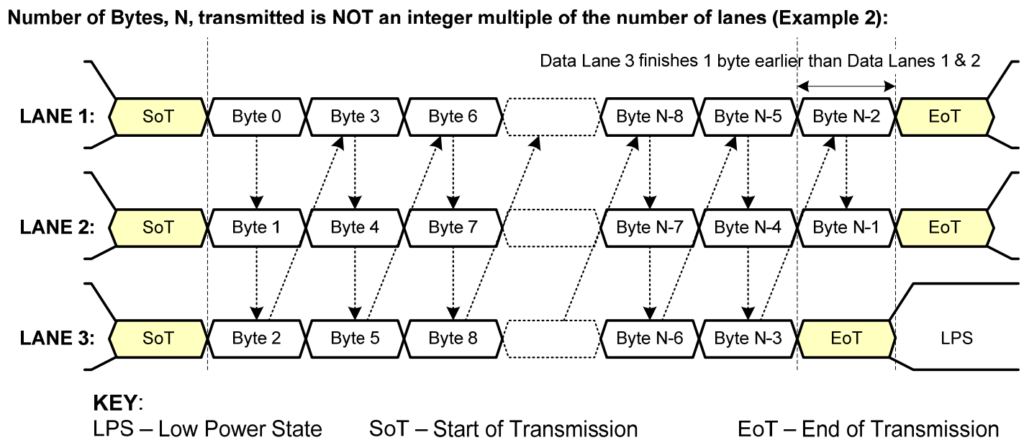

对于3个Lane,也有类似的情况:

4个Lane的情况也是类似的,这里就不详细描述了。综上所述,不管是何种情况(Lane的配置方式),每个Lane都同时开始SoT,并开始发送第一个字节,但是每个Lane的结束时间可能会相差一个字节的传输时间。