MIPI扫盲——D-PHY介绍(一)

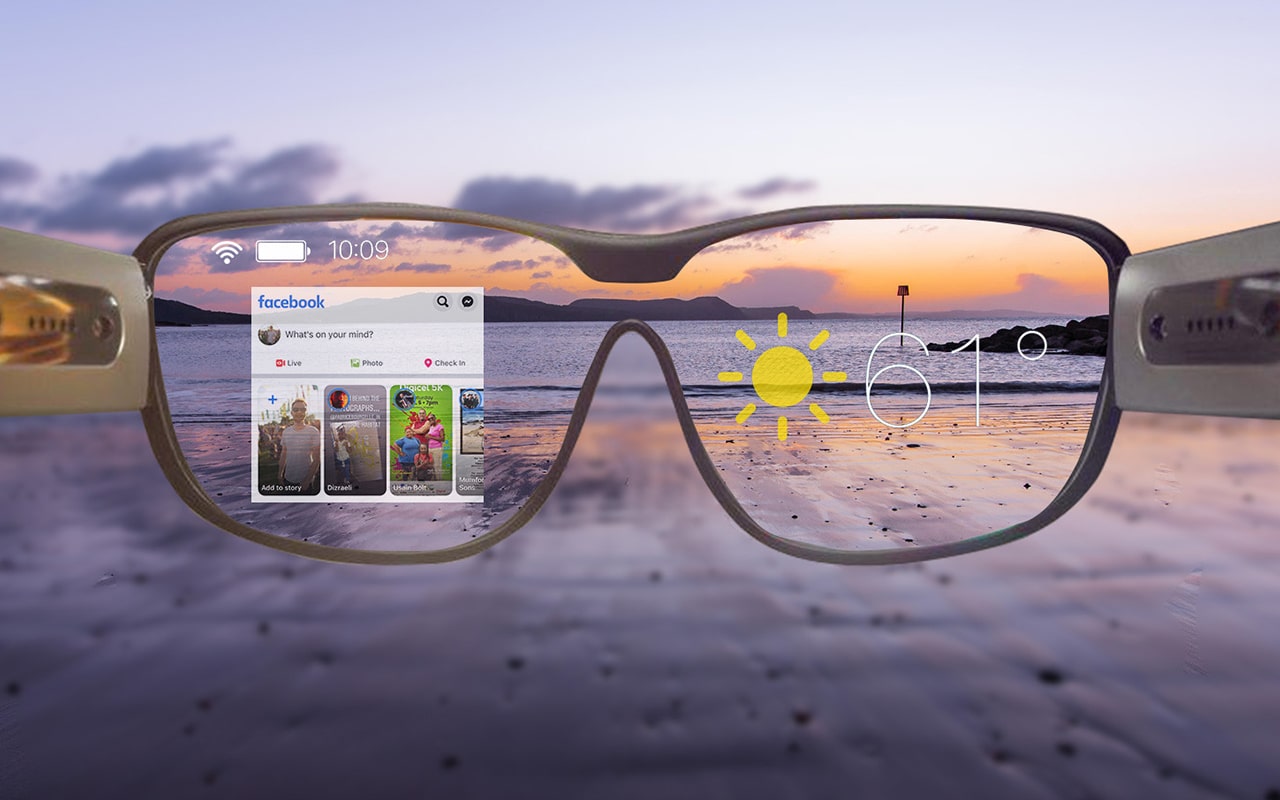

D-PHY种的PHY是物理层(Physical)的意思,那么D是什么意思呢?在MIPI D-PHY的文档中有提到过,D-PHY的最初版本的设计目标是500Mbits/s,而D是罗马数字(拉丁文数字)中500 。同理C和M分别是罗马数字中的100和1000,也就是C-PHY和M-PHY中C和M的意思了。 D-PHY是一种高速、低功耗的源同步物理层,由于采用了高功效设计,因此非常适合功耗大的电池供电设备使用。它里面同时包含了有助于实现高功效的高速模块和低功耗模块。载荷数据(图像数据)使用高速模块,控制和状态信息的发送(在照相机/显示器和应用处理器之间)使用的是低功耗模块(利用低频信号)。它具有在单个数据包脉冲中发送高速和低功耗数据的特殊能力。低功耗模块有助于节省功耗,高速模块则有助于实现高清晰度照片质量数据信号要求的较高带宽。 如下图所示,MIPI信号(HS模式下)相对于传统的TMDS信号、LVDS信号等,具有低电压摆幅,低功耗的优势。 MIPI D-PHY协议定义了两种传输模式:高速模式(High Speed,HS)和低功耗模式(Low Power,LP),两种模式使用不同的传输电平和传输机制。HS模式和LP模式的电平如下图所示: 使用示波器测量获得的HS波形如下图所示: 其中,HS模式下,为差分信号传输,信号电平在100mV~300mV(200mV的压摆);LP模式下,为单端信号传输,信号电平在0~1.2V(1.2V压摆)。HS模式下,信号传输速度可达80Mbps~1Gbps(v1.0)或80Mbps~1.5Gbps(v1.1),采用源同步的传输方式,由主机(Master)设备向从机(Slave)设备提供DDR时钟。LP模式下,信号传输速度为10Mbps,此时传输通道的差分线(HS模式下的)是两根独立的信号线。无论是HS模式还是LP模式,都采用LSB fisrt,MSB last的传输方式。 【注】为什么要这样设计?我个人的理解是这样的:HS模式下,信号传输速度较快,较低的压摆有利于提升传输速度,同时降低功耗和EMI;那么为什么LP模式下不用HS的传输机制呢?是因为LP模式下,传输的信号速度较慢,较低的压摆不利于系统的稳定(此时可能会有比较严重的过冲,如果采用100mV~300mV的电平的话)。 一个完整的MIPI传输系统结构图如下: 其中PHY Layer为物理层,如D-PHY,Low Level Protocol和Lane Management为中间层,如DSI和CSI,Application为应用层,可由软件或者硬件实现,以DSI系统为例,其中所有的命令需要符合MIPI的DCS(Display Command Set)规范。 D-PHY协议最多支持5个Lane(通道)(一个时钟Lane,4个数据Lane),最少需要两个Lane(一个时钟Lane,一个数据Lane)。 如上图所示,一个通用的Lane中包含LP-TX、LP-RX、HS-TX、HS-RX和LP-CD模块,所有收发模块均共用同一个差分线Dp,Dn(在LP模式下,为两根单独的信号线)。整个Lane通过PPI接口(PHY Protocol Interface)与系统的其他部分连接。 其中,LP-CD模块仅在存在于需要双向通信(Bidirectional)的系统中,对于不需要双向通信(Unidirectional)的系统,如CSI协议,则不需要LP-CD模块。显然,在Unidirectional系统中,主机(一般固定为Transmitter)则不需要RX模块,从机(一般固定为Receiver)则不需要TX模块。在需要双向通信的系统中,如DSI(当然,在特定的系统中,DSI也可以是Unidirectional的),一般只需要一个Data Lane具有双向收发的能力,其他的Data Lane和Clock Lane则可以根据实际需求,去除RX或者TX模块。需要注意的是,即使是在Bidirectional的系统中,Clock Lane也不需要反向传输,即当从机向主机发送数据时(反向传输),此时的时钟仍然是由主机提供(HS模式下,LP模式下则不需要时钟)。 比较有意思的地方是,在LP模式下(包括Control Mode和Escape Mode),采用的是Spaced-One-Hot Coding机制。在该机制下,时钟可以从传输的数据中得以体现,因此不需要传输时钟。此时,用户可以根据实际需求,设置Clock Lane继续运行或者关闭以降低功耗。关于Spaced-One-Hot Coding会在后面的博文中详细介绍。【注】我们常听到的LPDT模式(Low-Power Data Transmission)和ULPS模式(Ultra-Low Power State)都是Escape Mode的一种。 综上所述,也就是说,D-PHY中一共有三种Lane,Unidirectional Clock Lane 、Unidirectional Data Lane以及Bi-directional Data Lane。 需要注意的是,D-PHY的Bidirectional通信是一种半双工的双向通信模式,同时,反向传输的速度只有正向传输的1/4。 MIPI-Physical-Layers-M-PHY-D-PHY-C-PHY下载